Co to jest I2C

I2C to protokół szeregowy używany w dwuprzewodowym interfejsie do łączenia urządzeń o niskiej prędkości, takich jak mikrokontrolery, pamięci EEPROM, przetworniki A/D i D/A, interfejsy we/wy i inne podobne urządzenia peryferyjne w systemach wbudowanych. Jest to synchroniczna magistrala komunikacyjna typu multi-master, multi-slave z przełączaniem pakietów, single-ended, szeregowa magistrala komunikacyjna wynaleziona przez firmę Philips Semiconductors (obecnie NXP Semiconductors) w 1982 roku.

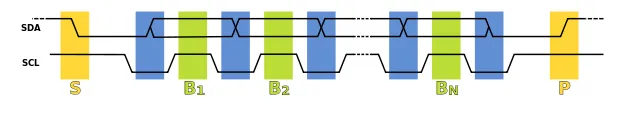

I²C wykorzystuje tylko dwa dwukierunkowe otwarte dreny (dane szeregowe (SDA) i zegar szeregowy (SCL)) i wykorzystuje rezystory do podciągania potencjału. I²C pozwala na znaczny zakres napięcia roboczego, ale typowy poziom napięcia wynosi +3.3 V lub +5 V.

Projekt referencyjny I²C wykorzystuje 7-bitową przestrzeń adresową, ale rezerwuje 16 adresów, dzięki czemu może komunikować się z maksymalnie 112 węzłami w grupie magistrali [a]. Wspólna magistrala I²C ma różne tryby: tryb standardowy (100 kbit/s), tryb niskiej prędkości (10 kbit/s), ale częstotliwość zegara może spaść do zera, co oznacza, że komunikacja może zostać zawieszona. Nowa generacja magistrali I²C może komunikować się z większą liczbą węzłów (obsługując 10-bitową przestrzeń adresową) z większą szybkością: tryb szybki (400 kbit/s), tryb szybki plus (1 Mbit/s), tryb szybki (3.4 Mbit /s), tryb ultraszybki (5 Mbit/s).

Co to jest I²S?

I²S (Inter-IC Sound) to standard interfejsu elektronicznej magistrali szeregowej używany do łączenia ze sobą cyfrowych urządzeń audio. Standard ten został po raz pierwszy wprowadzony przez firmę Philips Semiconductor w 1986 roku. Służy do przesyłania danych audio PCM pomiędzy obwodami scalonymi w urządzeniach elektronicznych.

Interfejs sprzętowy I2S:

1. Linia zegara bitowego

Formalnie nazywany „ciągłym zegarem szeregowym (SCK)”. Zwykle zapisywany jako „zegar bitowy (BCLK)”.

Oznacza to, że każdy bit danych odpowiadający dźwiękowi cyfrowemu SCLK ma impuls.

Częstotliwość SCLK = 2 × częstotliwość próbkowania × liczba bitów próbkowania.

2. Linia zegara słownego

Formalnie znany jako „wybór słów (WS)”. [Powszechnie określane jako „LRCLK” lub „Synchronizacja klatek (FS)”.

0 = lewy kanał, 1 = prawy kanał

3. Co najmniej jedna multipleksowana linia danych

Formalnie nazywane „danymi szeregowymi (SD)”, ale można je nazwać SDATA, SDIN, SDOUT, DACDAT, ADCDAT itp.

Schemat czasowy I²S