Што е I2C

I2C е сериски протокол што се користи за двожичен интерфејс за поврзување на уреди со мала брзина како што се микроконтролери, EEPROM, A/D и D/A конвертори, I/O интерфејси и други слични периферни уреди во вградените системи. Тој е синхрон, мулти-мајстор, мулти-слуга, префрлување пакети, единечен, сериски комуникациски автобус измислен од Philips Semiconductors (сега NXP Semiconductors) во 1982 година.

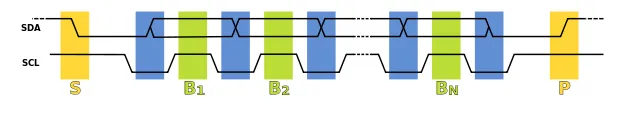

I²C користи само две двонасочни отворени одводи (сериски податоци (SDA) и сериски часовник (SCL)) и користи отпорници за да го зголеми потенцијалот. I²C овозможува значителен опсег на работен напон, но типичното ниво на напон е +3.3V или +5V.

Референтниот дизајн I²C користи 7-битен адресен простор, но резервира 16 адреси, така што може да комуницира со најмногу 112 јазли во група магистрали [a]. Вообичаената магистрала I²C има различни режими: стандарден режим (100 kbit/s), режим со мала брзина (10 kbit/s), но фреквенцијата на часовникот може да се дозволи да падне на нула, што значи дека комуникацијата може да се прекине. Новата генерација на I²C магистрала може да комуницира со повеќе јазли (поддржувајќи 10-битен адресен простор) со поголема брзина: брз режим (400 kbit/s), брз режим плус (1 Mbit/s), режим со голема брзина (3.4 Mbit /s), ултра брз режим (5 Mbit/s).

Што е I²S?

I²S (Inter-IC Sound) е стандарден интерфејс за електронски сериски автобус кој се користи за поврзување на дигитални аудио уреди, овој стандард првпат беше воведен од Philips Semiconductor во 1986 година. Се користи за пренос на аудио податоци PCM помеѓу интегрираните кола во електронските уреди.

Хардверски интерфејс I2S:

1. Линија на бит-такт

Формално наречен „Континуиран сериски часовник (SCK)“. Обично се пишува како „битен часовник (BCLK)“.

Односно, секој бит од податоци што одговара на дигитално аудио, SCLK има пулс.

Фреквенцијата на SCLK = 2 × фреквенција на земање примероци × број на битови за земање примероци.

2. Линија на часовник со зборови

Формално познат како „избор на зборови (WS)“. [Обично се нарекува „LRCLK“ или „Синхронизација на рамки (FS)“.

0 = лев канал, 1 = десен канал

3. Најмалку една мултиплексирана податочна линија

Формално наречен „Сериски податоци (SD)“, но може да се нарече SDATA, SDIN, SDOUT, DACDAT, ADCDAT итн.

Временски дијаграм на I²S