Qu'est-ce qu'I2C

I2C est un protocole série utilisé pour une interface à deux fils permettant de connecter des appareils à faible vitesse tels que des microcontrôleurs, des EEPROM, des convertisseurs A/D et D/A, des interfaces d'E/S et d'autres périphériques similaires dans les systèmes embarqués. Il s'agit d'un bus de communication série synchrone, multi-maître, multi-esclave, à commutation de paquets, asymétrique, inventé par Philips Semiconductors (maintenant NXP Semiconductors) en 1982.

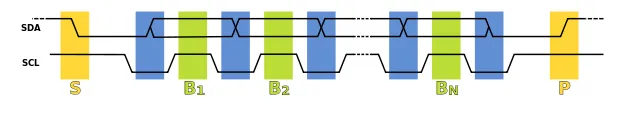

I²C utilise uniquement deux Open Drains bidirectionnels (données série (SDA) et horloge série (SCL)) et utilise des résistances pour augmenter le potentiel. I²C permet une plage de tension de fonctionnement considérable, mais le niveau de tension typique est de +3.3 V ou +5 V.

La conception de référence I²C utilise un espace d'adressage de 7 bits mais réserve 16 adresses, elle peut donc communiquer avec jusqu'à 112 nœuds dans un groupe de bus [a]. Le bus I²C commun a différents modes : mode standard (100 kbit/s), mode basse vitesse (10 kbit/s), mais la fréquence d'horloge peut descendre à zéro, ce qui signifie que la communication peut être suspendue. La nouvelle génération de bus I²C peut communiquer avec plus de nœuds (prenant en charge un espace d'adressage de 10 bits) à une vitesse plus rapide : mode rapide (400 kbit/s), mode rapide plus (1 Mbit/s), mode haut débit (3.4 Mbit/s). /s), mode ultra rapide (5 Mbit/s).

Qu’est-ce qu’I²S ?

I²S (Inter-IC Sound) est une norme d'interface de bus série électronique utilisée pour connecter des appareils audio numériques entre eux. Cette norme a été introduite pour la première fois par Philips Semiconductor en 1986. Elle est utilisée pour transférer des données audio PCM entre des circuits intégrés dans des appareils électroniques.

L'interface matérielle I2S :

1. Ligne d'horloge binaire

Anciennement appelée « Horloge série continue (SCK) ». Généralement écrit sous la forme « bit clock (BCLK) ».

Autrement dit, chaque bit de données correspondant à l'audio numérique, SCLK, possède une impulsion.

La fréquence de SCLK = 2 × fréquence d'échantillonnage × nombre de bits d'échantillonnage.

2. Ligne d'horloge de mots

Anciennement connu sous le nom de « sélection de mots (WS) ». [Communément appelé « LRCLK » ou « Frame Sync (FS) ».

0 = canal gauche, 1 = canal droit

3. Au moins une ligne de données multiplexée

Formellement appelé « Données série (SD) », mais peut être appelé SDATA, SDIN, SDOUT, DACDAT, ADCDAT, etc.

Chronogramme de I²S