¿Qué es I2C?

I2C es un protocolo serial utilizado para una interfaz de dos cables para conectar dispositivos de baja velocidad como microcontroladores, EEPROM, convertidores A/D y D/A, interfaces de E/S y otros periféricos similares en sistemas integrados. Es un bus de comunicación en serie síncrono, multimaestro, multiesclavo, de conmutación de paquetes, de un solo extremo, inventado por Philips Semiconductors (ahora NXP Semiconductors) en 1982.

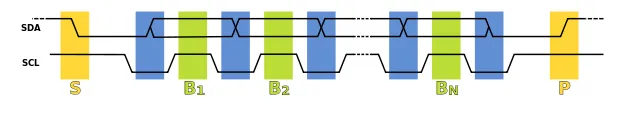

I²C solo usa dos Open Drains bidireccionales (datos en serie (SDA) y reloj en serie (SCL)) y usa resistencias para aumentar el potencial. I²C permite un rango de voltaje de funcionamiento considerable, pero el nivel de voltaje típico es +3.3 V o +5 V.

El diseño de referencia I²C utiliza un espacio de direcciones de 7 bits pero reserva 16 direcciones, por lo que puede comunicarse con hasta 112 nodos en un grupo de buses [a]. El bus I²C común tiene diferentes modos: modo estándar (100 kbit/s), modo de baja velocidad (10 kbit/s), pero se puede permitir que la frecuencia del reloj caiga a cero, lo que significa que se puede suspender la comunicación. La nueva generación de bus I²C puede comunicarse con más nodos (que admiten espacio de direcciones de 10 bits) a una velocidad más rápida: modo rápido (400 kbit/s), modo rápido plus (1 Mbit/s), modo de alta velocidad (3.4 Mbit/s). /s), modo ultrarrápido (5 Mbit/s).

¿Qué es I²S?

I²S (Inter-IC Sound) es un estándar de interfaz de bus serie electrónico que se utiliza para conectar dispositivos de audio digitales entre sí. Este estándar fue introducido por primera vez por Philips Semiconductor en 1986. Se utiliza para transferir datos de audio PCM entre circuitos integrados en dispositivos electrónicos.

La interfaz de hardware I2S:

1. Línea de reloj de bits

Formalmente llamado "Reloj serie continuo (SCK)". Generalmente se escribe como "reloj de bits (BCLK)".

Es decir, cada bit de datos correspondiente al audio digital, SCLK tiene un pulso.

La frecuencia de SCLK = 2 × frecuencia de muestreo × número de bits de muestreo.

2. Línea de reloj

Conocido formalmente como "selección de palabras (WS)". [Comúnmente conocido como "LRCLK" o "Frame Sync (FS)".

0 = canal izquierdo, 1 = canal derecho

3. Al menos una línea de datos multiplexada

Formalmente se llama "Datos serie (SD)", pero se puede llamar SDATA, SDIN, SDOUT, DACDAT, ADCDAT, etc.

Diagrama de tiempos del I²S